GXSC dual channel 14 bit 2.6GSPS high-speed analog-to-digital converter replaces AD9689 for application in communication receivers

Time:2026-01-08

Views:164

In modern communication fields such as 5G communication, satellite communication, software defined radio, and electronic countermeasures, broadband communication receivers need to have broadband coverage, high-speed signal capture, multi format compatibility, and low distortion processing capabilities to cope with increasingly complex electromagnetic environments and high-speed transmission requirements.

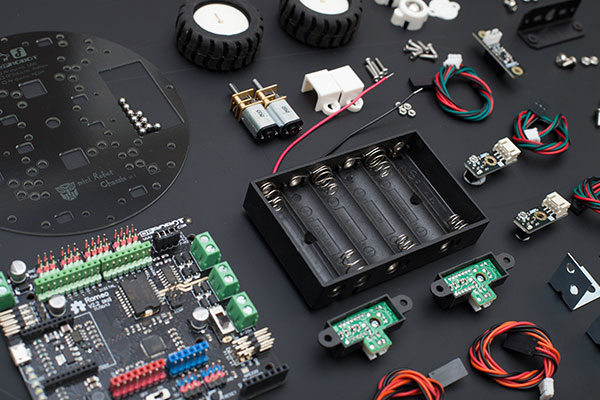

The analog-to-digital converter is the main component of the receiver RF link and digital signal processing unit. This article recommends a GXSC dual channel 14 bit 2.6GSPS high-speed analog-to-digital converter for application in communication receivers. The sampling rate, bandwidth, linearity, and integration of this chip can improve the receiving sensitivity, dynamic range, and signal processing efficiency of communication systems, thereby promoting the upgrade of communication systems to high bandwidth and high integration.

When capturing complex signals within a wide frequency range, broadband communication receivers undergo analog-to-digital conversion to complete signal demodulation, filtering, spectrum analysis, and other processing. This requires ultra wide analog bandwidth and high-speed sampling, and supports direct sampling of RF signals to simplify link design. The GXSC analog-to-digital converter supports direct sampling of RF signals up to 5GHz without the need for multi-level mixing links in traditional receivers, greatly simplifying hardware architecture and reducing link loss and noise introduction.

Its dual channel design supports a maximum sampling rate of 2.6GSPS, combined with a 14 bit resolution, which can accurately capture high-speed dynamic signals within a wide frequency range, avoiding signal aliasing and loss of details. This direct sampling capability not only improves the signal acquisition efficiency of the receiver, but also reduces system complexity and cost, providing core support for software defined radio architecture.

Chips have advantages such as large input bandwidth, high sampling rate, good linearity, small package size, and low power consumption. The dual channel ADC core adopts a multi-stage pipeline structure and integrates on-chip digital correction algorithms. Each ADC has a wide bandwidth input and supports various user selectable input ranges. Integrating a reference voltage source simplifies design complexity. The analog input and clock signal are differential inputs.

The GXSC also has several functions that can simplify the automatic gain control (AGC) of communication receivers. Programmable threshold detectors allow the use of fast detection control bits in ADC registers to monitor incoming signal power. In addition to fast detection output, it also provides signal monitoring capability. The signal monitoring module provides additional information about the digitized signal by the ADC. Users can configure subclass 1 high-speed serial output of base FJESD204B into multiple channel modes, including single channel, dual channel, four channel, and eight channel modes, based on data configuration and the acceptable channel data rate of the receiving logic device. ADC supports multi device synchronization through SYSREF+and SYNC INB ± input pins.

In addition, the chip has a flexible power-off mode that can achieve multiple low-power modes, all of which can be programmed using a 3-wire serial port interface (SPI).